La puerta OR proporcionan al diseñador del sistema implementación directa de la lógica positiva OR donde complementan las familias existentes de las puertas CMOS.

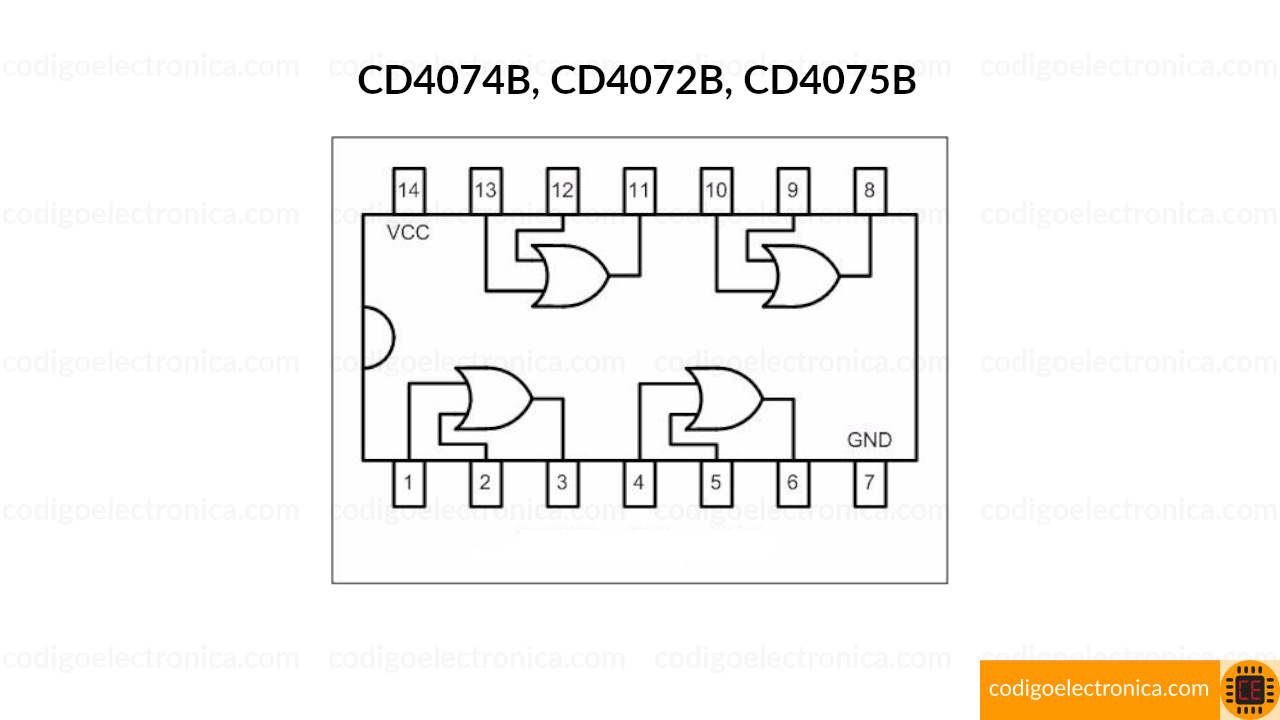

Los tipos CD4071B, CD4072B y CD4075B se suministran en paquetes cerámicos herméticos de doble línea de 14 derivaciones (sufijo F3A), paquetes de plástico de doble línea de 14 derivaciones (sufijo E), paquetes de 14 contornos pequeños de 14 derivaciones ( M, MT, M96 y NSR), y paquetes de contorno pequeño de 14 derivaciones delgadas (sufijos PW y PWR).

Características

- Velocidad media de operación de 60ns a VDD = 10V.

- Máxima corriente de entrada 1uA a 18V.

- Operación completamente estática.

- Calificaciones paramétricas de 5 V, 10 V y 15 V.

- Características de salida simétricas estandarizadas.

- Las entradas y salidas están protegidas contra efectos electrostáticos.

- Especificados de °40 °C a +85 °C y 40 °C a +125 C.

- Cumple con la norma JEDEC JESD 13-B.

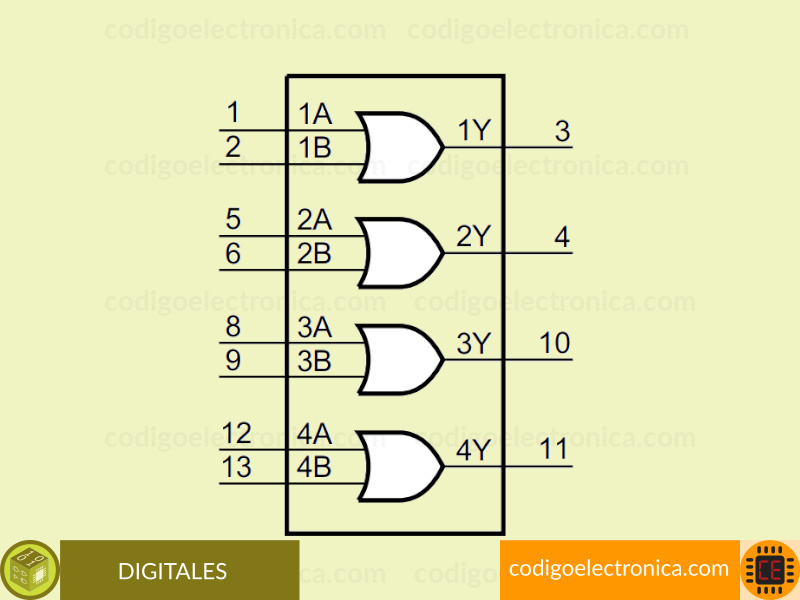

Diagrama de conexión

A continuación se muestra el diagrama de conexión del circuito 4071.[1]

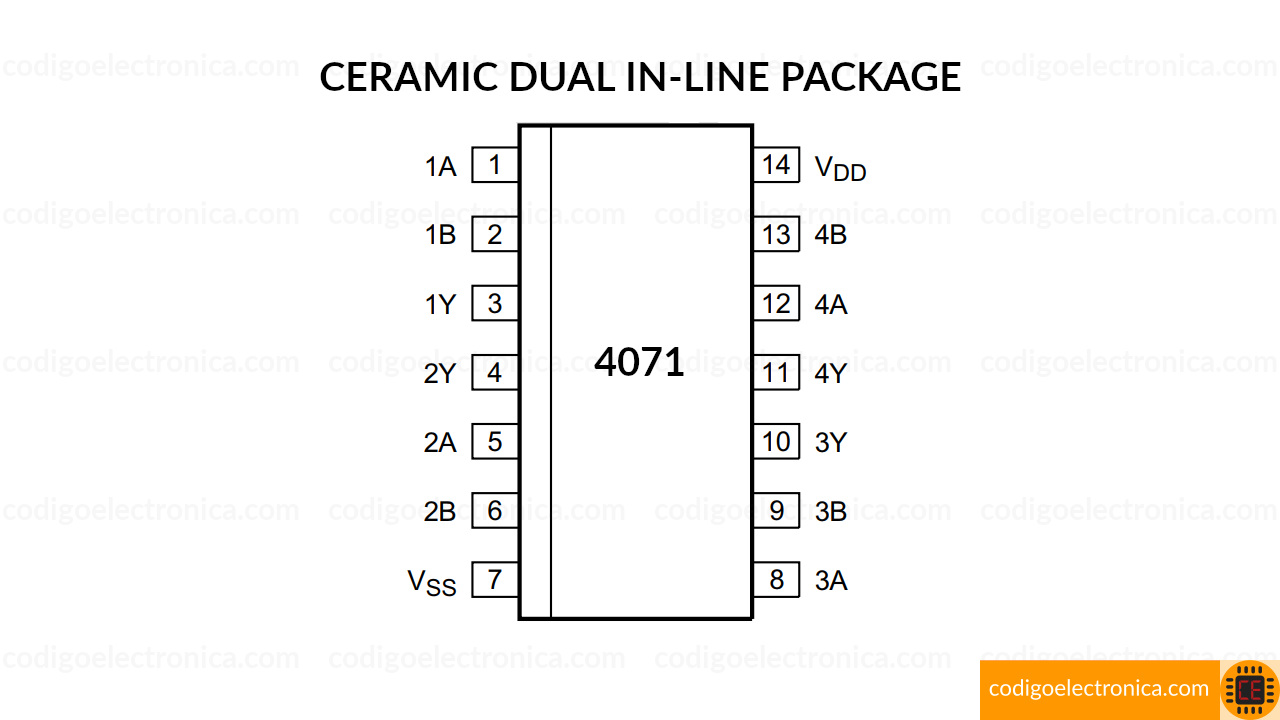

Pines de los chips

Esta es la distribución de los pines de cada encapsulado.

Tabla de verdad

Esta es la tabla de verdad que describe la lógica booleana de la OR, o suma booleana.

| Entradas | Salidas | |

|---|---|---|

| A | B | Y |

| L | L | L |

| L | H | H |

| H | L | H |

| H | H | H |

Condiciones recomendadas de uso

Se describen las condiciones de uso en temas de voltaje, corriente y temperatura.

| Símbolo | Parametro | Minimo | Maximo | Unidad |

|---|---|---|---|---|

| VDD | Voltaje de alimentación | 3 | 15 | V |

| VI | Voltaje de entrada | 0 | VDD | V |

| II | Corriente de entrada | - | 10 | mA |

| IO | Corriente de salida | - | 10 | mA |

| IDD | Corriente de alimentación | - | 50 | mA |

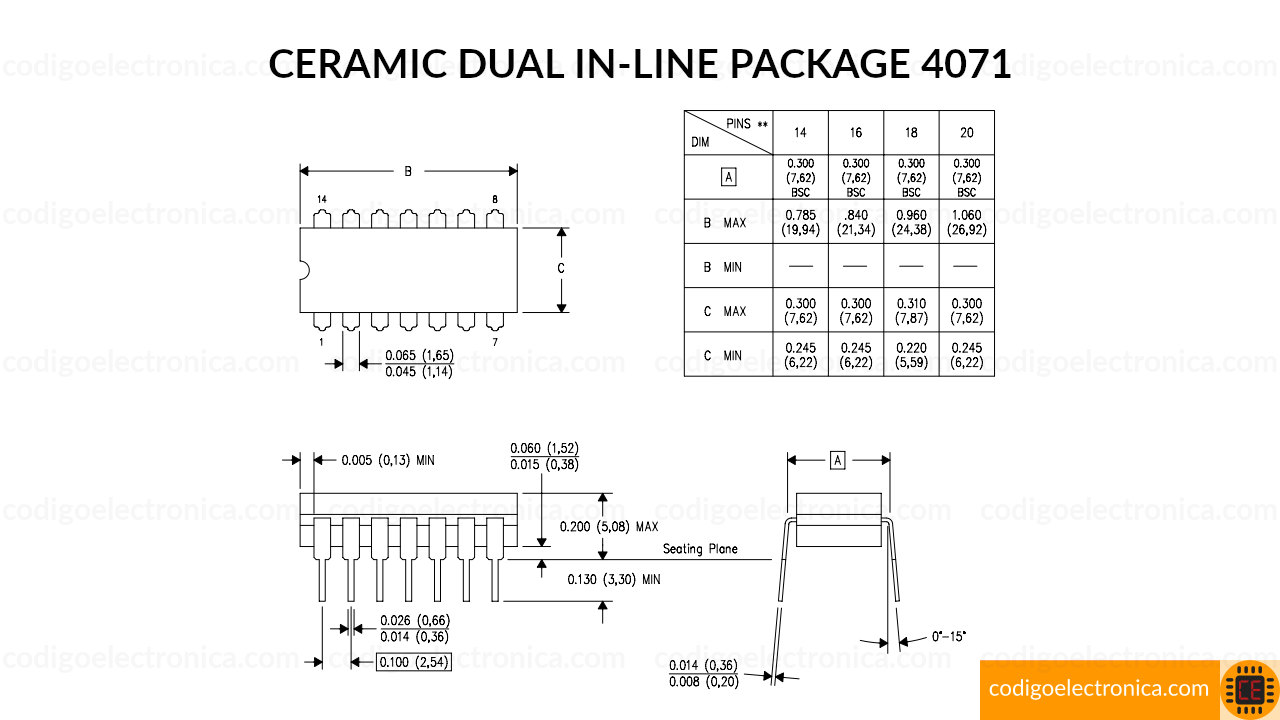

Dimensiones físicas

Se describen las dimensiones físicas de uno de los encapsulados.

Ver tambien

Referencias

[1] nexperia https://assets.nexperia.com/documents/data-sheet/HEF4071B.pdf, Consultado febrero 2019

[2] Texas Instruments http://www.ti.com/lit/ds/symlink/cd4071b-mil.pdf, Consultado febrero 2019